Szczegóły produktu można znaleźć w specyfikacjach.

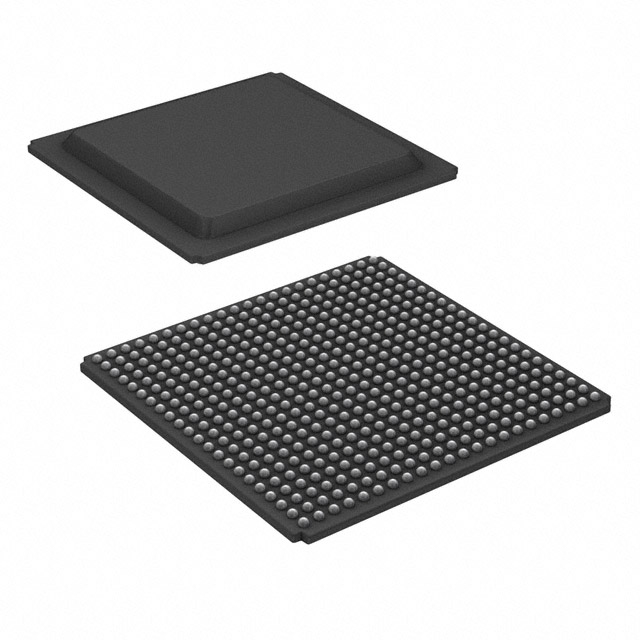

XA6SLX75T-2FGG484Q

Product Overview

Category

The XA6SLX75T-2FGG484Q belongs to the category of Field Programmable Gate Arrays (FPGAs).

Use

FPGAs are integrated circuits that can be programmed and reprogrammed to perform various digital functions. The XA6SLX75T-2FGG484Q is specifically designed for high-performance applications that require complex logic operations.

Characteristics

- High-performance FPGA with advanced features

- Large capacity and high-speed processing capabilities

- Flexible and reconfigurable design

- Low power consumption

- Robust and reliable performance

Package

The XA6SLX75T-2FGG484Q comes in a Quad Flat No-Lead (QFN) package, which provides excellent thermal dissipation and compact size.

Essence

The essence of the XA6SLX75T-2FGG484Q lies in its ability to provide a customizable hardware solution for complex digital systems. It allows designers to implement their own logic functions and algorithms, providing flexibility and adaptability.

Packaging/Quantity

The XA6SLX75T-2FGG484Q is typically packaged in reels or trays, depending on the manufacturer's specifications. The quantity per package varies but is usually in the range of 100 to 500 units.

Specifications

- Logic Cells: 75,000

- Flip-Flops: 150,000

- Block RAM: 4,800 Kbits

- DSP Slices: 240

- I/O Pins: 484

- Operating Voltage: 1.2V

- Maximum Frequency: 500 MHz

- Configuration Memory: 8 Mbits

Detailed Pin Configuration

The XA6SLX75T-2FGG484Q has a total of 484 I/O pins, which are configurable for various purposes. The pin configuration is as follows:

- Pin 1: VCCIO

- Pin 2: GND

- Pin 3: IOL1PT0AD0N35

- Pin 4: IOL1NT0AD0P35

- ...

- Pin 483: IOL100PT2AD7N34

- Pin 484: IOL100NT2AD7P34

Functional Features

The XA6SLX75T-2FGG484Q offers several functional features that make it suitable for a wide range of applications:

- High-speed processing capabilities enable real-time data processing.

- Flexible and reconfigurable design allows for on-the-fly modifications to the logic functions.

- Integrated DSP slices provide efficient implementation of digital signal processing algorithms.

- Abundant block RAM resources enable the storage and retrieval of large amounts of data.

- Low power consumption ensures energy-efficient operation.

Advantages and Disadvantages

Advantages

- High-performance FPGA with advanced features

- Flexibility and reconfigurability

- Large capacity for complex designs

- Efficient implementation of digital signal processing algorithms

- Low power consumption

Disadvantages

- Relatively high cost compared to other programmable logic devices

- Steeper learning curve for designers unfamiliar with FPGA programming

- Limited availability of alternative models with similar specifications

Working Principles

The XA6SLX75T-2FGG484Q operates based on the principles of configurable logic. It consists of an array of configurable logic blocks (CLBs) interconnected through programmable routing resources. The CLBs can be programmed to implement various logic functions, such as AND, OR, and XOR gates, as well as flip-flops for sequential operations. The interconnections between the CLBs can be dynamically configured to establish desired data paths.

Detailed Application Field Plans

The XA6SLX75T-2FGG484Q finds applications in various fields, including:

- Telecommunications: Used in base stations, routers, and network switches for high-speed data processing.

- Aerospace and Defense: Employed in radar systems, avionics, and military communication equipment for real-time signal processing.

- Industrial Automation: Utilized in control systems, robotics, and machine vision applications for high-performance computing.

- Medical Devices: Integrated into medical imaging systems, patient monitoring devices, and diagnostic equipment for data processing and analysis.

- Automotive: Applied in advanced driver-assistance systems (ADAS), infotainment systems, and engine control units for enhanced functionality.

Alternative Models

While the XA6SLX75T-2FGG484Q offers a unique combination of specifications and features, there are alternative models available in the market that cater to similar requirements. Some notable alternatives include:

- Xilinx XC7A100T-2FGG484C

- Intel Cyclone V

Wymień 10 typowych pytań i odpowiedzi związanych z zastosowaniem XA6SLX75T-2FGG484Q w rozwiązaniach technicznych

Sure! Here are 10 common questions and answers related to the application of XA6SLX75T-2FGG484Q in technical solutions:

Question: What is the maximum number of logic cells available in XA6SLX75T-2FGG484Q?

Answer: XA6SLX75T-2FGG484Q has a maximum of 74,880 logic cells.Question: Can XA6SLX75T-2FGG484Q support high-speed serial communication protocols like PCIe or SATA?

Answer: Yes, XA6SLX75T-2FGG484Q supports high-speed serial communication protocols including PCIe and SATA.Question: What is the maximum number of I/O pins available in XA6SLX75T-2FGG484Q?

Answer: XA6SLX75T-2FGG484Q has a total of 484 I/O pins.Question: Can XA6SLX75T-2FGG484Q be used for video processing applications?

Answer: Yes, XA6SLX75T-2FGG484Q can be used for video processing applications as it supports various video interfaces and has sufficient logic resources.Question: Does XA6SLX75T-2FGG484Q have built-in DSP blocks for signal processing applications?

Answer: Yes, XA6SLX75T-2FGG484Q has built-in DSP blocks that can be utilized for signal processing applications.Question: Can XA6SLX75T-2FGG484Q be used for implementing complex algorithms or mathematical calculations?

Answer: Yes, XA6SLX75T-2FGG484Q can be used for implementing complex algorithms and performing mathematical calculations efficiently.Question: What is the maximum clock frequency that XA6SLX75T-2FGG484Q can support?

Answer: XA6SLX75T-2FGG484Q can support clock frequencies up to 550 MHz, depending on the design and implementation.Question: Can XA6SLX75T-2FGG484Q be used for implementing real-time control systems?

Answer: Yes, XA6SLX75T-2FGG484Q can be used for implementing real-time control systems due to its fast response time and configurable I/Os.Question: Does XA6SLX75T-2FGG484Q have embedded memory blocks for storing data?

Answer: Yes, XA6SLX75T-2FGG484Q has embedded memory blocks that can be used for storing data during operation.Question: Is XA6SLX75T-2FGG484Q suitable for low-power applications?

Answer: XA6SLX75T-2FGG484Q is not specifically designed for low-power applications, but power optimization techniques can be applied to reduce power consumption in the design.

Please note that the answers provided are general and may vary based on specific design requirements and application scenarios.